Département d'Informatique Groupe de Recherche En Complexité et Cryptographie

# Implantation et optimisation des primitives cryptographiques

## THÈSE

présentée et soutenue publiquement le 25 Octobre 2001

pour l'obtention du

#### Doctorat Paris 7

par

Thomas Pornin

#### Composition du jury

Rapporteurs: Antoine Joux (DCSSI)

Jean-Jacques Quisquater (UCL – Louvain-la-Neuve)

Examinateurs: Guy Cousineau (LIAFA - Paris 7)

Henri Gilbert (France Telecom R&D) Jacques Stern (ÉNS / Directeur de Thèse)

Serge Vaudenay (ÉPFL - Lausanne)

Jean Vuillemin (ÉNS)

# Table des matières

| 1        | Intr           | $\mathbf{roduct}$                                                              | ion à la cryptographie conventionnelle                                                                                                                                                                                                                                             | 1                                                              |

|----------|----------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|          | 1.1            | Histor                                                                         | ique                                                                                                                                                                                                                                                                               | 1                                                              |

|          | 1.2            | Défini                                                                         | tions                                                                                                                                                                                                                                                                              | 2                                                              |

|          |                | 1.2.1                                                                          | Fonctions de chiffrement symétrique                                                                                                                                                                                                                                                | 2                                                              |

|          |                | 1.2.2                                                                          | Complexité d'une attaque                                                                                                                                                                                                                                                           | 4                                                              |

|          |                | 1.2.3                                                                          | Usage du chiffrement symétrique et sécurité                                                                                                                                                                                                                                        | 5                                                              |

|          | 1.3            | Descri                                                                         | ption de DES                                                                                                                                                                                                                                                                       | 7                                                              |

|          |                | 1.3.1                                                                          | Historique de DES                                                                                                                                                                                                                                                                  | 7                                                              |

|          |                | 1.3.2                                                                          | Structure de DES                                                                                                                                                                                                                                                                   | 7                                                              |

|          |                | 1.3.3                                                                          | Sécurité de DES                                                                                                                                                                                                                                                                    | 10                                                             |

|          | 1.4            | L'atta                                                                         | que de Davies et Murphy                                                                                                                                                                                                                                                            | 12                                                             |

|          |                | 1.4.1                                                                          | L'attaque originelle                                                                                                                                                                                                                                                               | 12                                                             |

|          |                | 1.4.2                                                                          | L'attaque améliorée                                                                                                                                                                                                                                                                | 17                                                             |

|          |                | 1.4.3                                                                          | Formalisation de l'attaque                                                                                                                                                                                                                                                         | 18                                                             |

|          | 1.5            | Concl                                                                          | usion                                                                                                                                                                                                                                                                              | 24                                                             |

|          |                |                                                                                |                                                                                                                                                                                                                                                                                    |                                                                |

| <b>2</b> | Imp            | olantat                                                                        | ions classiques sur processeurs génériques                                                                                                                                                                                                                                         | <b>25</b>                                                      |

| 2        | <b>Imp</b> 2.1 |                                                                                | ions classiques sur processeurs génériques<br>ités des processeurs polyvalents                                                                                                                                                                                                     | <b>25</b> 25                                                   |

| 2        | _              |                                                                                | ités des processeurs polyvalents                                                                                                                                                                                                                                                   |                                                                |

| 2        | _              | Capac                                                                          | ités des processeurs polyvalents                                                                                                                                                                                                                                                   | 25                                                             |

| 2        | _              | Capac<br>2.1.1                                                                 | ités des processeurs polyvalents                                                                                                                                                                                                                                                   | 25<br>26                                                       |

| 2        | _              | Capac<br>2.1.1<br>2.1.2                                                        | ités des processeurs polyvalents                                                                                                                                                                                                                                                   | 25<br>26<br>28                                                 |

| 2        | _              | Capac<br>2.1.1<br>2.1.2<br>2.1.3                                               | Les processeurs polyvalents                                                                                                                                                                                                                                                        | 25<br>26<br>28<br>31                                           |

| 2        | _              | Capace 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5                                           | Les processeurs polyvalents                                                                                                                                                                                                                                                        | 25<br>26<br>28<br>31<br>33                                     |

| 2        | 2.1            | Capace 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5                                           | Les processeurs polyvalents                                                                                                                                                                                                                                                        | 25<br>26<br>28<br>31<br>33<br>34                               |

| 2        | 2.1            | Capac<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>Impla                    | Les processeurs polyvalents                                                                                                                                                                                                                                                        | 25<br>26<br>28<br>31<br>33<br>34<br>35                         |

| 2        | 2.1            | Capac<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>Impla<br>2.2.1           | Les processeurs polyvalents                                                                                                                                                                                                                                                        | 25<br>26<br>28<br>31<br>33<br>34<br>35<br>35                   |

| 2        | 2.1            | Capac<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>Implat<br>2.2.1<br>2.2.2 | Les processeurs 8 bits                                                                                                                                                                                                                                                             | 25<br>26<br>28<br>31<br>33<br>34<br>35<br>35<br>36             |

| 2        | 2.1            | Capace 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5 Implate 2.2.1 2.2.2 2.2.3                 | Les processeurs polyvalents  L'âge d'or du CISC  L'avènement du RISC  La mémoire, poids mort de la vitesse  Résumé de la situation actuelle  ntation de DES sur Pentium  État de l'art  Détail des capacités du Pentium  Représentation des permutations                           | 25<br>26<br>28<br>31<br>33<br>34<br>35<br>35<br>36<br>37       |

| 2        | 2.1            | Capace 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5 Implair 2.2.1 2.2.2 2.2.3 2.2.4 2.2.5     | Les processeurs polyvalents  L'âge d'or du CISC  L'avènement du RISC  La mémoire, poids mort de la vitesse  Résumé de la situation actuelle  ntation de DES sur Pentium  État de l'art  Détail des capacités du Pentium  Représentation des permutations  La fonction de confusion | 25<br>26<br>28<br>31<br>33<br>34<br>35<br>35<br>36<br>37<br>39 |

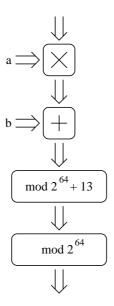

|   |      | 2.3.2 DFC                                         |

|---|------|---------------------------------------------------|

|   | 2.4  | Conclusion                                        |

| 3 | Bits | slice 51                                          |

|   | 3.1  | Principes fondamentaux du bitslice                |

|   |      | 3.1.1 Du câble au registre                        |

|   |      | 3.1.2 Conséquences opérationnelles                |

|   | 3.2  | Méthodes d'implantation du bitslice               |

|   |      | 3.2.1 Orthogonalisation des données               |

|   |      | 3.2.2 Orthogonalisation des tables                |

|   | 3.3  | Production automatique de code bitslice 61        |

|   |      | 3.3.1 Le langage de description d'algorithmes 61  |

|   |      | 3.3.2 Stratégie d'optimisation                    |

|   |      | 3.3.3 Évolution future de bsc                     |

|   | 3.4  | Chiffrement symétrique d'un disque dur            |

|   |      | 3.4.1 Conditions opérationnelles                  |

|   |      | 3.4.2 FBC                                         |

|   |      | 3.4.3 Implantation pratique de FBC                |

|   |      | 3.4.4 Sécurité de FBC                             |

|   |      | 3.4.5 Vérification de l'intégrité d'un disque dur |

|   | 3.5  | Conclusion                                        |

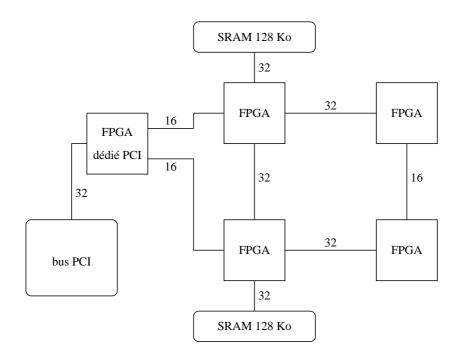

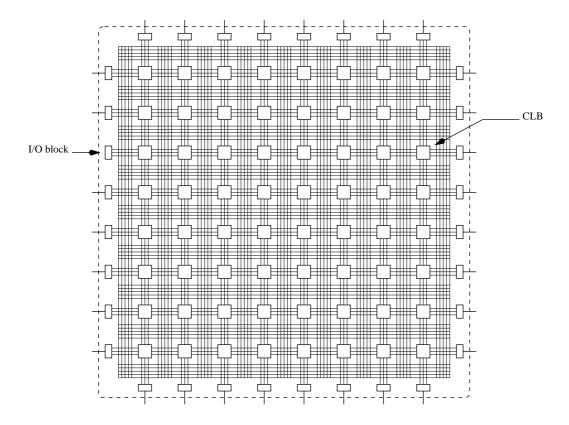

| 4 | FPO  | GA 81                                             |

|   | 4.1  | Présentation générale d'un FPGA                   |

|   | 4.2  | La carte Pamette                                  |

|   |      | 4.2.1 Vue d'ensemble                              |

|   |      | 4.2.2 FGPA Xilinx                                 |

|   |      | 4.2.3 Programmation                               |

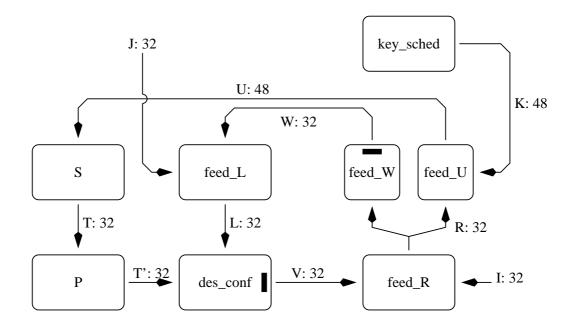

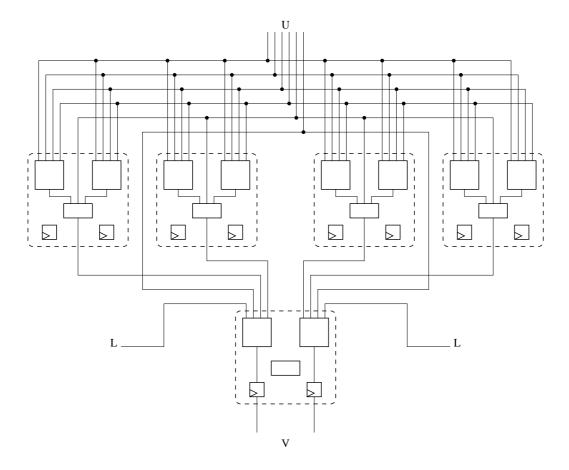

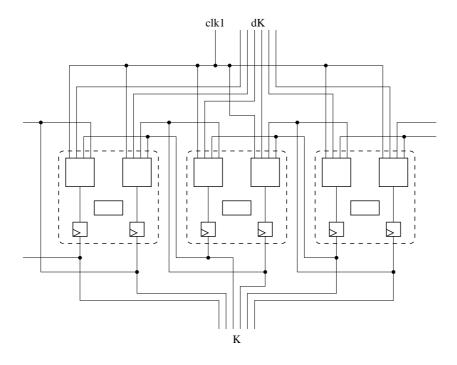

|   | 4.3  | DES-Cracker                                       |

|   |      | 4.3.1 Structure générale                          |

|   |      | 4.3.2 DES sur carte Pamette                       |

|   |      | 4.3.3 Mise en œuvre de la recherche               |

|   | 4.4  | Prospectives                                      |

|   |      | 4.4.1 La loi de Moore                             |

|   |      | 4.4.2 Gain pour les implantations matérielles 103 |

|   |      | 4.4.3 Le futur                                    |

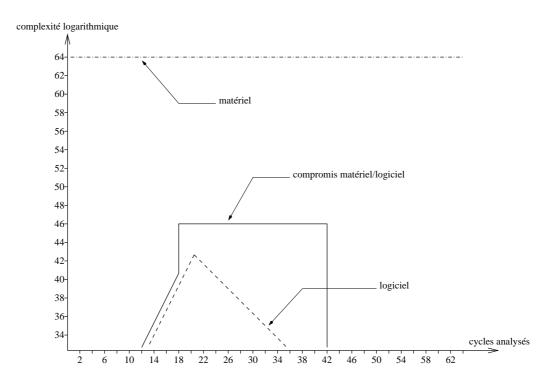

| 5 | Con  | npromis matériel/logiciel 107                     |

| • | 5.1  | , 3                                               |

|   | J.1  | 5.1.1 Historique de A5/1                          |

|   |      | 5.1.1 Historique de 119/1                         |

# TABLE DES MATIÈRES

| Bi | bliog | graphie                                     |  |       |   |  |       | 127 |

|----|-------|---------------------------------------------|--|-------|---|--|-------|-----|

| 6  | Cor   | nclusion                                    |  |       |   |  |       | 125 |

|    | 5.5   | Conclusion                                  |  | <br>• | • |  | <br>• | 123 |

|    |       | Compromis matériel/logiciel                 |  |       |   |  |       |     |

|    |       | 5.3.2 A5/1 et la recherche exhaustive       |  |       |   |  |       |     |

|    |       | 5.3.1 Implantation de $A5/1$ sur FPGA .     |  |       |   |  |       |     |

|    | 5.3   | Cryptanalyse matérielle de $A5/1$           |  |       |   |  |       |     |

|    |       | 5.2.2 Compromis flux/temps/mémoire .        |  |       |   |  |       | 115 |

|    |       | 5.2.1 Recherche exhaustive partielle        |  |       |   |  |       | 113 |

|    | 5.2   | Cryptanalyse logicielle de $A5/1$           |  |       |   |  |       | 112 |

|    |       | 5.1.4 Implantation de $A5/1$                |  |       |   |  |       | 11. |

|    |       | $5.1.3$ Mise en œuvre de $A5/1 \dots \dots$ |  |       |   |  |       | 110 |

|    |       |                                             |  |       |   |  |       |     |

# Remerciements

Je tiens à exprimer mes plus vifs remerciements envers, tout d'abord, Jacques Stern, qui a su, par son encadrement efficace, diriger mes travaux et me forcer à la rigueur et la précision scientifiques nécessaires à l'accomplissement de cette thèse. Je lui adresse toute ma gratitude pour m'avoir permis de travailler dans d'aussi bonnes conditions, et la confiance en mes capacités qu'il a témoignée. Je remercie également les membres actuels et passés du Groupe de Recherche En Complexité et Cryptographie, qui m'ont conseillé, aidé et supporté pendant plusieurs années; le GRECC possède une ambiance particulièrement adaptée à la recherche en cryptographie et au foisonnement des idées.

Je remercie particulièrement Serge Vaudenay, qui m'a fait découvrir la cryptographie et m'a initié aux algorithmes symétriques.

J'exprime toute ma gratitude à Jean Vuillemin, Mark Shand et Laurent Moll, qui m'ont permis de jouer avec leurs FPGA, m'ont patiemment expliqué comment m'en servir, et avec qui j'ai eu de longues discussions fructueuses.

Je remercie chaleureusement Éric Brunet, expert en LATEX, et patient et méticuleux relecteur, tout comme Évelyne Prioux.

Je remercie mes rapporteurs, Antoine Joux et Jean-Jacques Quisquater, qui ont lu et commenté ma prose, ainsi que Guy Cousineau, Henri Gilbert, Serge Vaudenay et Jean Vuillemin, qui ont accepté de faire partie de mon jury.

Un grand merci à Joëlle et Valérie, qui déchargent quotidiennement les chercheurs des soucis administratifs, et au SPI, qui transforme les ordinateurs en outils utilisables.

Merci enfin à mes parents, sans qui ma vie ne serait pas vraiment ce qu'elle est actuellement, et à tous ceux que dans mon inconséquence j'ai malencontreusement oubliés.

# Résumé

La cryptographie symétrique est l'étude des algorithmes de chiffrement de données, dont la clé de déchiffrement est identique à la clé de chiffrement. Ces algorithmes servent à rendre inintelligible une information, sauf pour les détenteurs d'une certaine convention secrète, afin de permettre son transfert sur des lignes de communication potentiellement espionnées, voire activement corrompues. Cette thèse s'intéresse au problème de l'implantation et de l'optimisation de ces algorithmes sur divers matériels informatiques, incluant les ordinateurs génériques et les FPGA (circuits reprogrammables). Les algorithmes classiques (DES, RC4, A5/1...) sont abordés, ainsi que des variantes de ces algorithmes afin de mieux s'adapter au matériel, sans sacrifier la sécurité; une nouvelle technique de programmation, dite « bitslice » ou « code orthogonal », est décrite, ainsi que les outils semi-automatiques de support de cette technique. Enfin, il est montré comment une utilisation adéquate de FPGA, en complément de stations de travail, permet d'accélérer grandement des travaux de cryptanalyse.

# Abstract

Symmetric cryptography is the science of algorithms enciphering and deciphering data with the same secret key. Those algorithms are used to obfuscate data and make it unreadable to anyone but those who hold the key and can de-obfuscate the data and return it to its original layout; thus, they allow safe data transfers through unsafe and potentially hostile networks. This thesis is about the implementation and optimization of such algorithms on various devices, including generic purpose workstations and FPGAs (reprogrammable chips). The standard algorithms such as DES, RC4, A5/1 are studied, as well as other variations designed to match closely the intended supporting hardware, without sacrificing security. A new implementation technique, called "bitslice" or "orthogonal code", is described, along with an automatic tool to support such coding. Finally, this work explains how a fine-tuned mix between FPGA and generic workstations can greatly enhance cryptanalysis efficiency.

# Chapitre 1

# Introduction à la cryptographie conventionnelle

# 1.1 Historique

La cryptographie est, historiquement, l'art de cacher une information pour la rendre inintelligible à toute personne ne connaissant pas un certain secret. Les applications de la cryptographie remontent à la plus haute antiquité, et son usage est aussi ancien que celui de l'écriture; on a retrouvé la trace de méthodes de chiffrement utilisées en Haute Égypte. Ces méthodes étaient pratiquées par l'intermédiaire d'appareils rudimentaires, voire par une simple opération de substitution mentale; la sécurité du système était alors empiriquement définie par l'échec de ceux qui tentaient d'en percer les secrets.

Longtemps chasse gardée des militaires, la cryptographie commence à sortir de l'ombre vers la fin du XIX<sup>e</sup> siècle. Mais la révolution principale en la matière a lieu à la fin des années trente, peu avant et pendant la seconde guerre mondiale. Les dispositifs cryptographiques sont alors de complexes assemblages d'engrenages et de relais électriques, dont le mécanisme est un secret jalousement surveillé. Afin de contrer les modèles allemands, les services secrets brittaniques développent, en 1936, des méthodes d'analyse systématique, et surtout un appareil électronique permettant de mener à bien ces analyses; cet appareil, premier vrai ordinateur jamais construit, est le Colossus[77], et il ouvre la porte à une nouvelle ère : désormais, la cryptographie est une science et devient une branche de l'informatique. L'histoire de ces temps héroïques du chiffrement, depuis l'usage de hiéroglyphes spéciaux jusqu'à la cryptanalyse de la machine allemande Enigma, est décrite en détail dans l'ouvrage majeur de David Kahn, *The codebreakers*[47].

L'après-guerre a vu le développement des algorithmes cryptographiques

modernes, à la sécurité quantifiée, analysée, partiellement prouvée, ainsi que le transfert définitif de la cryptologie dans la recherche publique. De nouveaux axes de recherche sont apparus, qui traitent de problèmes divers, tels que la réalisation d'une signature électronique, la vérification de l'intégrité d'un document informatique, l'authentification, etc.

Un changement des mentalités est également intervenu. Autrefois, quand Jules César assiégeait Avaricum¹ et devait envoyer ses ordres secrets à ses différentes légions, le plus important était la confidentialité des ordres; la difficulté d'écriture et de lecture des ordres par l'émetteur et le destinataire légitime était secondaire. Le système utilisé était primitif (chaque lettre était décalée de trois rangs dans l'alphabet) mais efficace en ces temps-là. Désormais, la cryptographie est une aide à la réalisation de la sécurité informatique; son rôle est d'empêcher les fraudes et piratages passifs ou actifs. En tant qu'outil de prévention, elle n'est pas le but du système informatique, mais plutôt un mal nécessaire. Les outils cryptographiques modernes se doivent d'être discrets, voire transparents. Leur efficacité informatique prime; le défi posé aux cryptographes est de réaliser une sécurité satisfaisante et convaincante, en n'utilisant qu'une faible partie de la puissance du matériel informatique devant être protégé.

### 1.2 Définitions

#### 1.2.1 Fonctions de chiffrement symétrique

Les systèmes de chiffrement modernes travaillent sur des données binaires; on manipule toujours des suites de bits. Une permutation indexée par une clé est une fonction définie ainsi :

$$E: \mathcal{M} \times \mathcal{K} \longrightarrow \mathcal{M}$$

$$(M, K) \longmapsto E(M, K)$$

$$(1.1)$$

où  $\mathcal{M}$  est un ensemble de mots binaires d'une certaine taille n qu'on appelle « messages », et  $\mathcal{K}$  est dénommé « espace des clés ». Cette fonction doit accepter une fonction inverse D définie comme suit :

$$D: \mathcal{M} \times \mathcal{K} \longrightarrow \mathcal{M}$$

$$(M, K') \longmapsto D(M, K')$$

$$(1.2)$$

telle que pour toute clé K, il existe une clé K' telle que, pour tout élément M de  $\mathcal{M}$ , on ait :

$$D(E(M, K), K') = E(D(M, K'), K) = M$$

(1.3)

$<sup>^{1}</sup>$ Bourges

Autrement dit, pour chaque clé K, E doit réaliser une permutation de l'ensemble  $\mathcal{M}$  des messages.

Un système de chiffrement symétrique est une permutation indexée par une clé telle que :

- l'application de cette permutation à un message est calculable aisément par un algorithme prenant en entrée le message et la clé K (dite de chiffrement);

- l'application de la permutation inverse est tout aussi calculable algorithmiquement, si la clé K' (de déchiffrement) est connue;

- la clé K est identique à la clé K';

- sans la connaissance de la clé K, la fonction de chiffrement est computationnellement indistinguable d'une permutation aléatoire.

Ce dernier point mérite quelques éclaircissements. On suppose le modèle suivant (utilisé, par exemple, dans [60]) :

- On dispose de quatre « boîtes noires », c'est-à-dire des appareils au fonctionnement opaque, prenant en entrée des messages M de l'espace  $\mathcal{M}$  des messages et donnant en sortie des messages du même espace.

- Les boîtes vont par paires et réalisent chacunes des permutations de l'ensemble  $\mathcal{M}$  des messages; chaque boîte d'une paire est la permutation inverse de l'autre boîte de la même paire.

- L'une des paires de boîtes implante un système de chiffrement symétrique utilisant une certaine clé K choisie aléatoirement et uniformément dans l'espace  $\mathcal{K}$  des clés; l'autre paire calcule une permutation choisie aléatoirement et uniformément dans l'espace des permutations de  $\mathcal{M}$ .

Une personne, dénommée l'attaquant, doit tenter de reconnaître la paire de boîtes implantant la fonction de chiffrement de celle calculant la permutation choisie aléatoirement. L'attaquant connaît tous les détails de l'algorithme de chiffrement recherché, mais ignore tout de la clé. Il peut faire fonctionner les boîtes sur un grand nombre d'entrées, mais possède une puissance computationnelle bornée (aussi bien en temps qu'en mémoire). Le système de chiffrement est dit computationnellement indistinguable d'une permutation aléatoire si l'attaquant ne peut pas deviner laquelle des paires de boîtes implante la fonction de chiffrement avec une probabilité substantiellement différente de 1/2. Une procédure d'attaque permettant de briser cette indistinguabilité est appelée un distingueur. Cette « procédure » est un algorithme utilisant éventuellement une source d'aléa externe.

#### 1.2.2 Complexité d'une attaque

La complexité du travail de l'attaquant peut être mesurée suivant le travail calculatoire nécessaire, la nature et le nombre des accès aux boîtes noires, et la probabilité de succès. Les messages présentés à la boîte de chiffrement sont des messages clairs; la sortie de cette boîte fournit des messages chiffrés. On notera que tout élément de l'ensemble  $\mathcal{M}$  des messages est à la fois un message clair et un message chiffré, suivant le contexte.

- La complexité en temps est mesurée en fonction du nombre d'instances de l'algorithme de chiffrement qui auraient pu être exécutées sur le même matériel dans le même temps. La complexité en mémoire est la taille en bits, octets ou toute autre unité, du stockage nécessaire à la réalisation de l'attaque.

- Si les requêtes de l'attaquant ne portent que sur des messages clairs ou chiffrés choisis aléatoirement et uniformément, l'attaque est dite à clair connu.

- Si les requêtes de l'attaquant sont des messages clairs choisis spécifiquement et envoyés à la boîte de chiffrement, l'attaque est dite à clair choisi.

- Si les requêtes de l'attaquant sont des messages chiffrés choisis spécifiquement et envoyés à la boîte de déchiffrement, l'attaque est dite à chiffré choisi.

- Si l'attaquant peut émettre toutes ses requêtes en un point de son calcul, recevoir ensuite toutes les réponses, puis terminer son attaque sans aucune autre requête, alors l'attaque est dite non adaptative.

La distinction entre les clairs choisis et les chiffrés choisis ne se fait pas dans le modèle explicité plus haut; en revanche, cette dinstinction peut se faire dans le contexte d'une utilisation réelle d'un système de chiffrement.

L'attaque la plus générique contre un système de chiffrement symétrique est la recherche exhaustive. C'est une attaque à clair connu nécessitant très peu de requêtes à la boîte de chiffrement. Le principe est très simple : il s'agit d'essayer toutes les clés possibles, jusqu'à en trouver une qui « marche ». Pour contrer cette attaque, il faut que l'esapce de clés soit suffisamment large pour que son parcours soit computationnellement infaisable. Des données plus précises sur ce qui est à la portée de la technologie actuelle seront données dans la section 4.4.

5

#### 1.2.3 Usage du chiffrement symétrique et sécurité

#### Utilisation d'un algorithme de chiffrement

La principale utilisation du chiffrement symétrique est d'assurer la confidentialité d'un canal de communication. Deux entités, traditionnellement appelées « Alice » et « Bob » (et notées A et B), partagent un secret commun qu'elles utilisent sous la forme d'une clé de chiffrement. Alice chiffre les données qu'elle veut envoyer à Bob, qui peut les déchiffrer grâce à sa connaissance de la clé. Si un attaquant, Ève² (notée E), écoute la conversation, elle ne pourra en tirer aucune information sans la connaissance de la clé.

Un usage détourné est l'authentification : Alice veut prouver son identité à Bob; pour cela, Bob lui envoie un message clair, et Alice doit retourner le message chiffré correspondant, suivant la clé secrète connue d'Alice et Bob seulement. Sans la connaissance de cette clé, une fausse Alice ne peut pas réaliser cette opération.

Si le chiffrement symétrique permet de réaliser la confidentialité et une certaine forme d'authentification, des besoins plus avancés tels que la signature électronique (qui permet d'assurer l'intégrité d'un message, ce qui contre les attaques actives, où Eve modifie les données transmises) demandent l'utilisation de primitives cryptographiques plus évoluées, où les clés de chiffrement et de déchiffrement sont non seulement différentes, mais aussi telles qu'il n'est pas computationnellement possible de calculer l'une en fonction de l'autre. Ces systèmes de chiffrement asymétriques utilisent des objets algébriques hautement structurés, et, s'ils sont fonctionnellement beaucoup plus riches que les fonctions de chiffrement symétriques, ils sont aussi beaucoup plus lourds en temps de calcul et moins souples d'utilisation dans des contextes à fortes contraintes (cartes à puce, canaux de communication lents, etc). Aussi, les protocoles modernes de sécurité mettent en œuvre des combinaisons d'algorithmes symétriques et asymétriques. Ces derniers sont souvent désignés sous le terme générique de « clé publique » et ne sont pas traités dans cette thèse.

#### Sécurité par transparence

On peut se demander pourquoi il est considéré que l'attaquant a accès à tous les détails de l'algorithme; lui donner ce genre d'information ne peut en effet que l'aider. Il est cependant généralement considéré que conserver un système de chiffrement secret diminue la sécurité, pour les raisons suivantes :

- L'algorithme existe toujours sous une forme implantée, donc tangible

<sup>&</sup>lt;sup>2</sup>De l'anglais *eavesdropper*, espion.

- et potentiellement interceptable et analysable; seule une clé peut rester à l'abri dans un cerveau humain. Il est donc sage de considérer que l'attaquant a, de toutes façons, accès aux détails de l'algorithme employé.

- L'analyse d'un algorithme de chiffrement est une opération très délicate; publier les détails d'un algorithme, c'est s'assurer le concours de centaines de chercheurs en cryptographie de par le monde.

- La clé concentre le secret ; en cryptographie symétrique, la clé est quasiment toujours un mot binaire de taille fixée, et tous les mots de cette taille sont des clés valides. Ceci permet de chiffrer simplement le coût de la recherche exhaustive de la clé ; une telle recherche sur les algorithmes serait beaucoup plus difficile à estimer.

Le fait de conserver les détails de l'algorithme secrets est appelé habituellement « sécurité par obscurité », et est considéré comme une très mauvaise approche du problème de la sécurité informatique en général.

#### Sécurité empirique et preuves

La sécurité des systèmes de chiffrement symétrique est encore globalement empirique. On peut distinguer plusieurs classes d'attaques et concevoir des algorithmes dont la structure peut être prouvée résistante à de telles attaques; on le verra notamment dans la suite de ce chapitre, pour le cas de l'algorithme DES.

Mais, de façon générale, le seul critère de sécurité connu est d'avoir résisté à une analyse publique par la communauté de recherche en cryptographie pendant plusieurs années. Afin de se donner plus de confiance, on considère qu'un algorithme n'est sûr que s'il résiste même à des attaques irréalistes, dites « académiques ». En effet, dans la pratique, il n'est pas raisonnable de supposer que l'attaquant dispose d'une mémoire plus grande que le système solaire, ou peut faire chiffrer par sa cible des camions entiers de bandes magnétiques contenant des données soigneusement choisies par lui. Mais la résistance à de telles conditions est considérée comme une preuve de compétence de la part du concepteur de l'algorithme, ce qui permet non seulement d'avoir un système de sécurité inattaqué, mais surtout d'être préalablement assuré de ce fait.

En résumé, la sécurité d'un protocole cryptographique est une affaire de prévision de risques et de confiance.

## 1.3 Description de DES

#### 1.3.1 Historique de DES

DES signifie Data Encryption Standard. Le développement de ce standard a été lancé en 1972; il s'agissait de proposer un algorithme efficace, implantable facilement sur du matériel à bas coût, validable, versatile, et suffisamment sûr pour être proposé comme algorithme « universel » de chiffrement pour l'industrie et l'administration américaines (sauf les communications classées secrètes, dont l'utilisation et le transfert sont beaucoup plus encadrés).

Le NBS (National Bureau of Standards, devenu ensuite le NIST, National Institute of Standards and Technology) a lancé deux appels d'offre, en 1973 et 1974; IBM a envoyé comme réponse au second l'algorithme Lucifer[80]. Le NBS, IBM et la NSA (National Security Agency) ont ensuite collaboré pour modifier l'algorithme (afin, officiellement, d'augmenter sa sécurité) et régler quelques détails juridiques (IBM avait un brevet sur Lucifer). L'algorithme obtenu a été publié en 1975, et la norme elle-même[29] a été rendue publique en 1977.

Le DES est aussi connu sous le nom de DEA (*Data Encryption Algo-rithm*), selon la dénomination de l'ANSI (*American National Standards Institute*)[27].

#### 1.3.2 Structure de DES

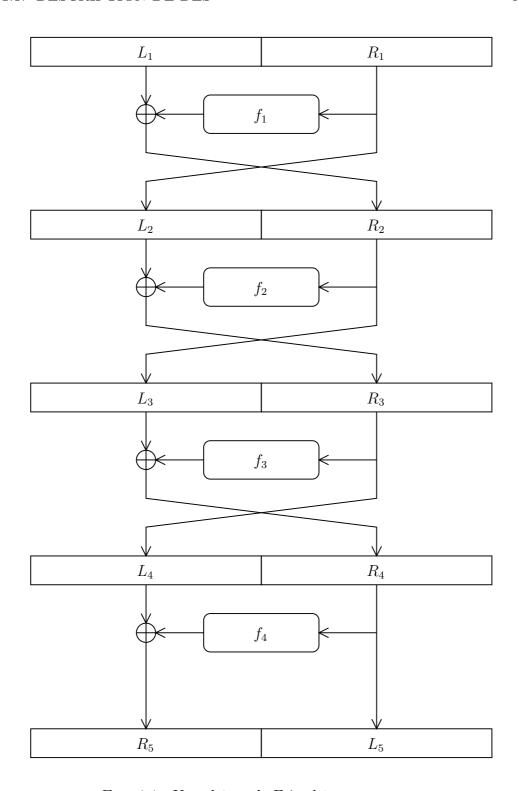

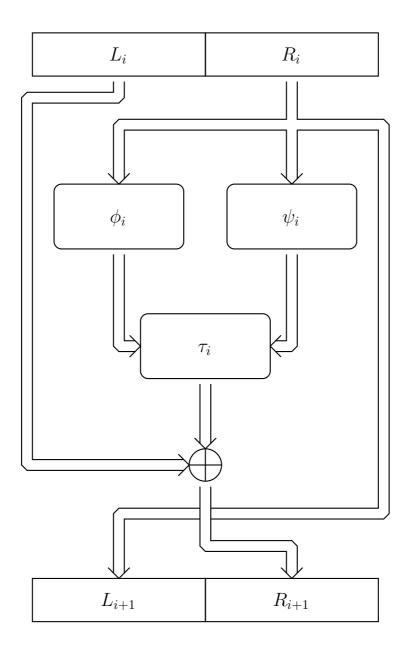

La structure générale de DES est un schéma de Feistel, du nom du concepteur de l'algorithme Lucifer[34]. Ce schéma utilise un certain nombre de tours (16, dans le cas de DES) et permet de réaliser une permutation de l'espace des messages clairs dans l'espace des messages chiffrés, telle que la permutation inverse soit facilement implantable, et même, dans une large mesure, partage une partie de l'implantation de la première permutation.

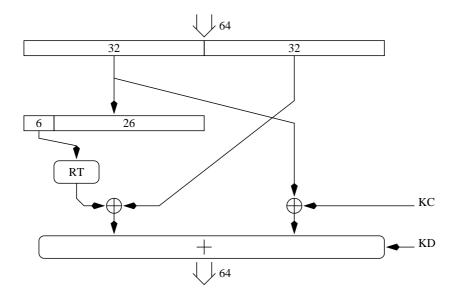

On travaille sur des blocs de données binaires de largeur paire 2n (dans le cas de DES, 2n = 64); l'entrée du tour i est découpée en deux moitiés de taille n, la partie gauche  $L_i$  et la partie droite  $R_i$ . Une fonction  $f_i$ , dite « de confusion », prenant une entrée de taille n et une sortie de même taille, est utilisée à chaque tour. Cette fonction n'a pas besoin d'être inversible, et elle est en général indexée par une clé. La sortie du tour i, qui est aussi l'entrée du tour i + 1, est définie ainsi :

$$L_{i+1} = R_i \tag{1.4}$$

$$R_{i+1} = L_i \oplus f_i(R_i) \tag{1.5}$$

Autrement dit, la moitié gauche est combinée par un OU EXCLUSIF avec le résultat de la fonction  $f_i$  appliquée à la moitié droite; puis les deux moitiés sont échangées.

Il est facile de voir que ce tour est inversible; l'inverse se calcule ainsi :

$$R_i = L_{i+1} \tag{1.6}$$

$$L_i = R_{i+1} \oplus f_i(L_{i+1}) \tag{1.7}$$

Dans le cas de DES, le texte clair subit d'abord une permutation fixe de ses bits (c'est la permutation IP), et le texte chiffré est égal au permuté par la permutation inverse  $IP^{-1}$  de la sortie du dernier tour après échange des deux moitiés de cette sortie; cet échange supplémentaire (qui n'est pas spécifique à DES) permet de rendre le déchiffrement très similaire au chiffrement (seul l'ordre d'usage des fonctions de confusion  $f_i$  change). La figure 1.1 illustre un schéma de Feistel à quatre tours.

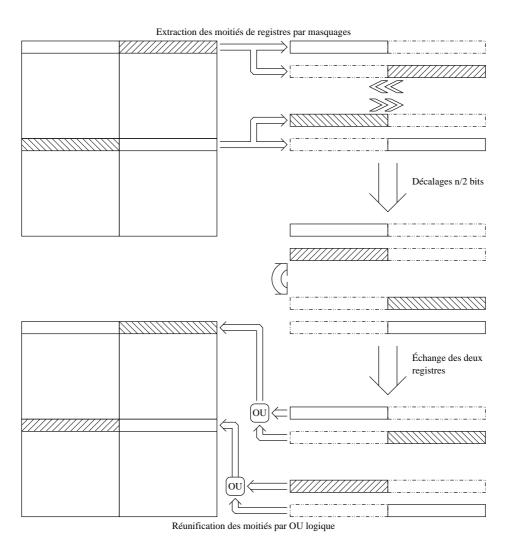

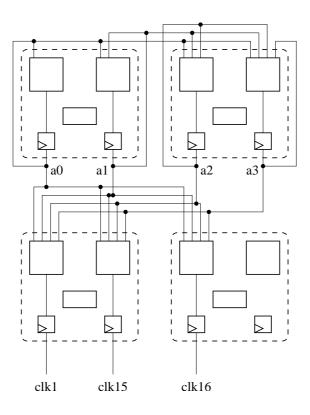

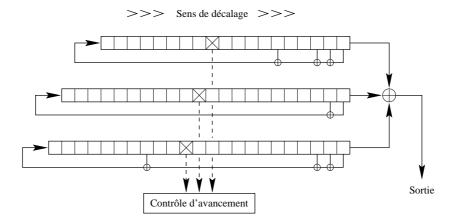

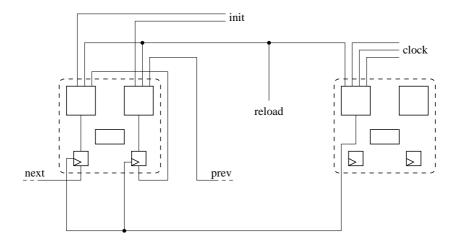

Les 16 fonctions de confusions de DES sont toutes identiques, à ceci près qu'elles utilisent chacune une clé de 48 bits, et que ces clés sont différentes pour les 16 tours. Ces 16 clés sont extraites de la clé maître (qui a une taille de 56 bits) suivant la méthode suivante : la clé maître est placée dans deux registres à décalage de 28 bits; pour chaque tour, les deux registres sont décalés d'un ou deux bits (suivant le tour concerné), puis les 48 bits sont copiés depuis 48 des 56 bits formés par ces deux registres; cette extraction est la même pour tous les tours. Ces registres sont adaptés à une implantation matérielle; les implantations logicielles ont tendance à simplement définir par des tables la provenance exacte, dans la clé maître, de chaque bit de chaque sous-clé.

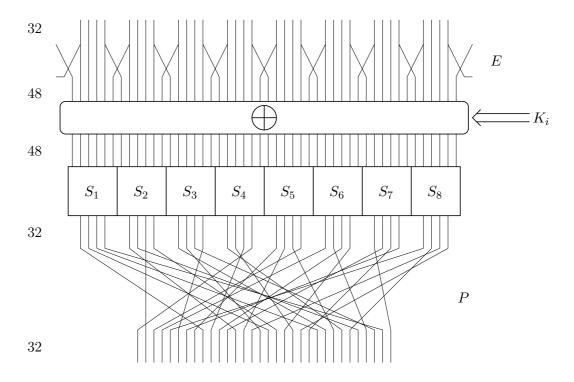

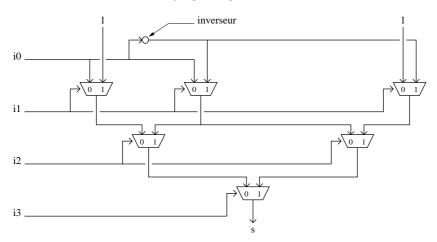

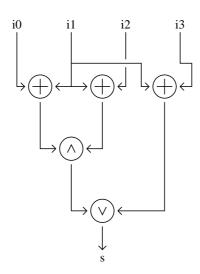

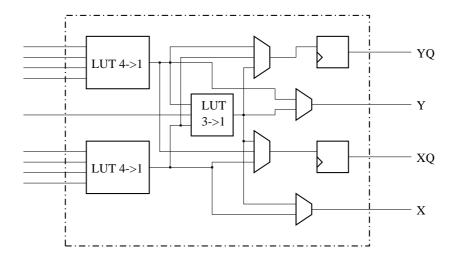

La fonction de confusion de DES est constituée des phases suivantes :

- l'entrée, sur 32 bits, est étendue à 48 bits (c'est l'expansion E) par duplication de certains bits;

- cette valeur de 48 bits est combinée par OU EXCLUSIF avec la sous-clé  $K_i$  du tour;

- les 48 bits résultants sont regroupés en 8 mots de 6 bits;

- chacun des mots de 6 bits sert d'entrée à une table, nommée boîte S, dont la sortie est un mot de 4 bits; il y a 8 boîtes S différentes;

- les 8 sorties de 4 bits des boîtes S sont concaténées pour former un mot de 32 bits;

- ces 32 bits sont permutés suivant la permutation fixe P.

Ce processus est illustré par la figure 1.2; seule la sous-clé  $K_i$  change dans les différents tours de DES.

Les boîtes S sont des tables spécifiées dans la norme de DES[29]. Leur sortie est équilibrée; pour toute valeur donnée de leurs deux bits d'entrée

Fig. 1.1 : Un schéma de Feistel à quatre tours

Fig. 1.2: La fonction de confusion de DES

extrêmes, chaque boîte S se comporte comme une permutation de l'ensemble des mots binaires de 4 bits formant ses 4 entrées centrales.

Comme on le verra dans les chapitres suivants, DES est particulièrement adapté aux implantations matérielles, mais est peu efficace en logiciel. Les permutations initiale et finale  $(IP \ et \ IP^{-1})$ , par exemple, n'ont pas de justification cryptographique (étant fixes, elles sont aisément inversibles par tout attaquant) mais représentent exactement l'échange d'un mot de 64 bits entre un bus de données de largeur 8 bits, et huit registres à décalages de 8 bits; autrement dit, elles permettent une implantation matérielle plus efficace, avec moins de latence et de silicium utilisé, dans ce genre de situation.

#### 1.3.3 Sécurité de DES

La sécurité de DES est un sujet qui a été longuement étudié depuis la publication de sa norme; le développement de DES ayant été confidentiel, il a longtemps été suggéré qu'il était possible qu'une faiblesse (une « back-door ») ait été introduite volontairement par la NSA, afin de permettre le déchiffrement rapide par cette institution de messages chiffrés en DES. Lors d'une présentation à Crypto'2000[20], Don Coppersmith, un des membres

de l'équipe de développement de DES, a assuré que la NSA n'a pas altéré le développement de DES, mais a plutôt constaté que l'équipe d'IBM avait redécouvert quelques méthodes d'attaques de cryptosystèmes dont la NSA avait jusqu'alors le secret. DES a été prévu pour contrer ces attaques, et non pour y céder.

Les seules attaques connues à ce jour sur DES sont :

- la recherche exhaustive de la clé;

- la cryptanalyse différentielle;

- la cryptanalyse linéaire;

- l'attaque dite de Davies et Murphy.

La recherche exhaustive de la clé est rendue possible par la faible longueur de cette dernière: en effet, si la clé fait stricto sensu 64 bits, seuls 56 bits sont utilisés effectivement, les 8 autres étant ignorés et pouvant servir de contrôle de parité. Une propriété de complémentation de DES (si on inverse chaque bit du texte clair et de la clé, le chiffré obtenu est également l'inverse bit à bit du chiffré précédent) permet de diviser par deux, sous certaines conditions, le coût de cette attaque. Cette recherche exhaustive a été effectuée plusieurs fois, aussi bien en logiciel[31] que sur du matériel spécialisé (cf. section 4.3).

La cryptanalyse différentielle a été découverte en 1990 par Eli Biham et Adi Shamir[9, 13, 12] puis appliquée à de nombreux autre cryptosystèmes (par exemple Feal[10], Lucifer[4], des versions réduites de RC5[50], etc). Des variantes de la cryptanalyse différentielle (différentielles impossibles[8], différentielles tronquées[49], attaques « boomerangs »[86]) ont aussi été proposées. Toutes ces méthodes reposent, schématiquement, sur l'idée d'analyser des paires de couples clair/chiffré, en « suivant » les différences binaires entre deux textes clairs, ou entre deux textes chiffrés, le long de l'algorithme. Dans le cas de DES, une attaque utilisant 2<sup>47</sup> couples clair/chiffré choisis par l'attaquant permet de retrouver la clé. Le temps d'analyse est certes plus court qu'une recherche exhaustive de la clé, mais les conditions opérationnelles (l'attaquant doit faire chiffrer par sa victime 2<sup>47</sup> mots de 64 bits qu'il a choisis, c'est-à-dire un million de giga-octets) sont telles que cette attaque est peu réaliste. Don Coppersmith à déclaré[19, 20] que l'équipe de développement de DES avait déjà connaissance de la cryptanalyse différentielle en 1975, et avait particulièrement renforcé les boîtes S contre cette attaque; en tous cas, il a été constaté[12, 11] que de subtils changements des boîtes S rendaient quasiment toujours le DES plus fragile face à la cryptanalyse différentielle. On notera que le fait que les cryptanalyses différentielles soient souvent impossibles à tester ouvre la porte à des erreurs; ainsi, une cryptanalyse de l'algorithme Skipjack[51] a été publiée en 1999, puis prouvée erronée par Louis Granboulan en 2001[41].

En 1993, Mitsuru Matsui a publié [62, 63] une nouvelle attaque nommée

cryptanalyse linéaire qui, dans le cas de DES, permet une attaque ne nécessitant la connaissance « que » de 2<sup>43</sup> couples clair/chiffré, qui n'ont pas besoin d'être choisis spécifiquement par l'attaquant. Cela représente quelques 65 000 giga-octets de données, et autant pour leur version chiffrée, ce qui rend cette attaque guère plus réaliste que la précédente. Son principe est d'établir une équation linéaire entre certains bits du texte clair, du texte chiffré et de la clé, qui soit vraie avec une probabilité différente de 0,5; l'analyse de nombreux couples clair/chiffré permet de découvrir le OU EXCLUSIF des bits de clé concernés. La variante présentée dans [63] combine ces équations linéaires avec la fonction de confusion de DES et permet de retrouver 26 bits secrets d'un seul coup (les 30 autres étant trouvés par une recherche exhaustive en quelques heures sur une simple station de travail).

La cryptanalyse linéaire a été essayée sur d'autres algorithmes; des liens entre les cryptanalyses linéaire et différentielle ont été exhibés[17], ce qui explique que DES résiste relativement bien à la cryptanalyse linéaire, puisqu'il a été consolidé contre la cryptanalyse différentielle. La résistance à une classe englobant ces deux attaques a été formalisée par Serge Vaudenay sous le nom de théorie de la décorrélation[83], puis plus particulièrement dans le cas des schémas de Feistel[84].

La structure même des schémas de Feistel a été largement étudiée dans un cadre plus général que DES et Lucifer; il a été montré dans [60] qu'avec des fonctions de confusion « parfaites » suivant certains critères, ce schéma permettait de construire un cryptosystème symétrique prouvé sûr. Des variations sur le schéma de Feistel ont aussi été étudiées et utilisées; par exemple, les fonctions de hachage MD5[65] et SHA-1[78] utilisent des schémas de Feistel étendus, où les données en cours sont découpées en respectivement quatre et cinq blocs.

L'attaque de Davies et Murphy sera étudiée en détail dans la section suivante.

# 1.4 L'attaque de Davies et Murphy

## 1.4.1 L'attaque originelle

L'attaque de Davies et Murphy a d'abord été présentée dans [26] puis améliorée par Eli Biham et Alex Biryukov dans [7]. L'attaque originelle utilise une propriété commune aux schémas de Feistel; en utilisant les notations de la section 1.3.2, pour tout tour i (sauf le dernier), nous avons les deux

13

équations suivantes :

$$f_i(R_i) = L_i \oplus R_{i+1} \tag{1.8}$$

$$R_{i+1} = L_{i+2} (1.9)$$

ce qui nous donne ceci:

$$f_i(R_i) = L_i \oplus L_{i+2} \tag{1.10}$$

Ceci est vrai pour tous les tours sauf le dernier. On peut effectuer le OU EXCLUSIF de ces équations pour les tours pairs, et pour les tours impairs; après simplification, on obtient les deux équations suivantes :

$$R \oplus L' = \bigoplus_{i=1}^{r/2} f_{2i}(R_{2i})$$

$$L \oplus R' = \bigoplus_{i=1}^{r/2} f_{2i-1}(R_{2i-1})$$

$$(1.11)$$

$$L \oplus R' = \bigoplus_{i=1}^{r/2} f_{2i-1}(R_{2i-1})$$

(1.12)

pour le cas d'un schéma de Feistel à r tours, r pair, où (comme dans le cas de DES et de la figure 1.1) les deux moitiés de la sortie du dernier tour sont échangées. L et R sont les moitiés gauche et droite de l'entrée (c'est-à-dire que  $L = L_1$  et  $R = R_1$ ) et L' et R' sont les moitiés gauche et droite de la sortie  $(L' = R_{r+1} \text{ et } R' = L_{r+1}).$

Autrement dit, chaque couple clair/chiffré nous donne accès au OU EX-CLUSIF des sorties des fonctions de confusion des étages pairs, ainsi qu'à celui des sorties des fonctions de confusion des étages impairs. Si un motif non uniformément distribué apparaît dans la sortie des fonctions de confusion, cette propriété pourrait permettre de faire apparaître ce biais après analyse d'un grand nombre de couples clair/chiffré; si ce biais est dépendant de la clé, une information sur cette dernière pourrait ainsi être obtenue. C'est le principe même de l'attaque de Davies et Murphy.

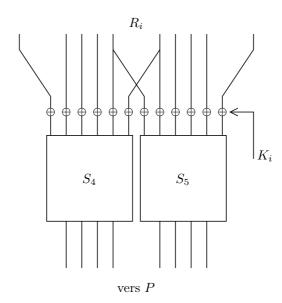

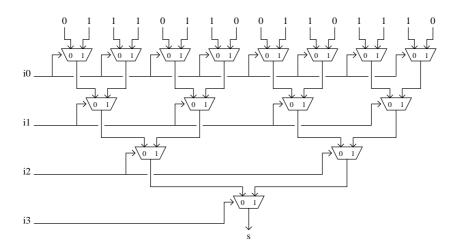

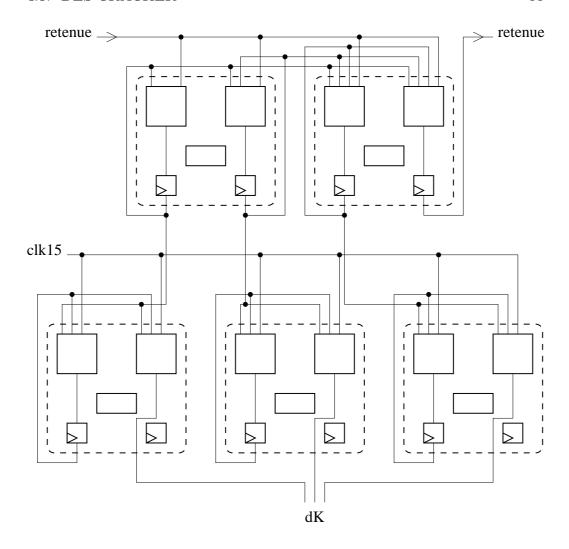

Considérons le cas de la fonction de confusion du tour i de DES; sa sortie est le permuté par P (qui est une permutation fixée dans la norme et identique pour tous les tours) des sorties des boîtes S. Si on considère deux boîtes S voisines: leurs deux sorties combinées forment un mot de 8 bits, dépendant de 12 bits d'entrée; or, si 12 bits de  $K_i$  interviennent dans cette entrée, seuls 10 bits de  $R_i$  y ont une influence. La figure 1.3 illustre ce fait.

Deux bits d'entrée sont dupliqués, et chacun est combiné avec deux bits différents de la sous-clé  $K_i$ , c'est-à-dire deux bits de la clé maître de DES (puisque chaque bit de chaque sous-clé est en fait un bit de la clé maître). Suivant le OU EXCLUSIF des deux bits de clé combinés avec les deux instances d'un bit dupliqué, les deux entrées correspondantes de la paire de boîtes S

Fig. 1.3 : Deux boîtes S voisines de DES

seront donc toujours identiques, ou toujours différentes. Comme il y a deux bits dupliqués, ce sont deux OU EXCLUSIF de deux bits de clés qui déterminent quel ensemble de  $2^{10} = 1024$  entrées possibles pour la paire de boîtes S sera effectivement parcouru sur un grand nombre de couples clair/chiffré.

Ainsi, potentiellement, la sortie de deux boîtes S voisines présentera, en sortie de la fonction de confusion de chaque tour, un motif parmi quatre, ce motif étant dépendant de la clé. Du fait de la définition même des boîtes S et de l'égalité de ces boîtes et de la permutation P au cours de l'algorithme, il n'y a en fait que deux distributions possibles du OU EXLUSIF de la sortie de deux boîtes S voisines sur plusieurs tours de DES; le choix entre ces deux distributions est directement dépendant du OU EXCLUSIF de plusieurs bits de la clé. Des détails sur ce calcul peuvent être trouvés dans [26].

L'attaque est alors menée ainsi : l'attaquant collecte de nombreuses paires clair/chiffré et calcule, pour chacune, le OU EXCLUSIF de la sortie de deux boîtes S voisines sur les tours pairs, et aussi sur les tours impairs. Il établit, dans chaque cas, la distribution choisie grâce à la méthode statistique dite du « maximum de vraisemblance » ; synthétiquement, cette méthode revient à choisr la distribution qui a le plus de chances de donner le résultat mesuré. Comme on peut travailler indépendamment sur les tours pairs et sur les tours impairs, on obtient ainsi deux bits « indirects » de la clé (un bit indirect est une combinaison linéaire de plusieurs bits ; c'est une information aussi valable que la connaissance d'un vrai bit pour ce qui est de la recherche exhaustive du reste de la clé).

Mathématiquement, comme on travaille sur un motif de 8 bits, pouvant prendre 256 valeurs, on représente les deux distributions possibles comme deux vecteurs u et v de  $\mathbf{R}^{256}$ ;  $u_i$ , la i-ème coordonnée de u ( $0 \le i \le 255$ ) est la probabilité d'obtenir la sortie i. Trivialement, ces coordonnées sont toutes des nombres réels positifs dont la somme vaut 1 pour chaque vecteur. On définit aussi les vecteurs u' et v' qui sont les déviations de u et v par rapport aux distributions uniformes, c'est-à-dire que :

$$\forall i \in \{0..255\}, \ u_i = \frac{1}{256} + u_i' \tag{1.13}$$

$$v_i = \frac{1}{256} + v_i' \tag{1.14}$$

Nous avons donc:

$$\sum_{i=0}^{255} u_i' = 0 \tag{1.15}$$

$$\sum_{i=0}^{255} v_i' = 0 \tag{1.16}$$

Par ailleurs, du fait de la définition des boîtes S, on a la propriété suivante (qui n'est pas générique aux schémas de Feistel) :

$$u' + v' = 0 (1.17)$$

Supposons que nous possédons M paires clair/chiffré indépendantes; parmi ces M paires, chaque valeur i du motif de 8 bits apparaît  $m_i$  fois. Si la distribution théorique est u, la probabilité d'un tel événement est proche de :

$$p_1 = \prod_{i=0}^{255} u_i^{m_i} \tag{1.18}$$

On définit de même  $p_2$  dans le cas de v. Comparer  $p_1$  et  $p_2$  est équivalent à comparer leurs logarithmes :

$$\log p_1 = \sum_{i=0}^{255} m_i \log u_i \tag{1.19}$$

On a donc:

$$\log p_1 = \sum_{i=0}^{255} m_i \log(\frac{1}{256} + u_i') \tag{1.20}$$

d'où:

$$\log p_1 = \sum_{i=0}^{255} m_i \log(1 + 256u_i') - M \log 256$$

(1.21)

car la somme des  $m_i$  est M. Comme chaque  $u'_i$  est petit devant 1/256 (car DES ne présente pas de biais statistique flagrant, et le biais recherché n'apparaît qu'après analyse d'un grand nombre de couples clair/chiffré), on peut remplacer les logarithmes par leur développement limité autour de 1, et obtenir les deux équations suivantes :

$$\log p_1 + M \log 256 \approx 256 \sum_{i=0}^{255} m_i u_i'$$

(1.22)

$$\log p_2 + M \log 256 \approx 256 \sum_{i=0}^{255} m_i v_i' \tag{1.23}$$

Nous ramenons donc l'attaque à la comparaison des deux valeurs suivantes :

$$s_1 = \sum_{i=0}^{255} m_i u_i' \tag{1.24}$$

$$s_2 = \sum_{i=0}^{255} m_i v_i' \tag{1.25}$$

Ces deux valeurs,  $s_1$  et  $s_2$ , sont le produit scalaire de m avec u' et celui de m avec v'. Nous pouvons majorer ces produits scalaires en utilisant la norme euclidienne sur  $\mathbf{R}^{256}$ . Si on note N(x) la norme euclidienne de x, nous avons :

$$s_1 = m \cdot u' \le N(m)N(u') \tag{1.26}$$

$$s_2 = m \cdot v' \le N(m)N(v') \tag{1.27}$$

m est le résultat de l'analyse de paires clair/chiffré; ce vecteur suit donc une distribution précise, mais peut varier autour de cette distribution. Chaque  $m_i$  compte le nombre d'occurrences de la valeur i pour le motif de huit bits; cette valeur est proche de M/256 car la distribution de la valeur du motif est proche de la distribution uniforme (si cette distribution était très éloignée de la distribution uniforme, DES serait un fort mauvais cryptosystème). Donc la variance de  $m_i$  est proche de (M/256)(255/256), que nous approchons par M/256.

Donc, la différence entre m et sa valeur théorique (valeur qui est M fois le vecteur de distribution) est un vecteur dont les coordonnées sont des valeurs de l'ordre de  $(\sqrt{M})/16$ ; donc la norme de ce vecteur de déviation est en

moyenne  $\sqrt{M}$ . La norme de m, quant à elle, est proche de M/16. Pour conclure quoi que ce soit des paires clair/chiffré, la déviation recherchée (la différence entre  $s_1$  et  $s_2$ ) ne doit pas être plus petite que la déviation naturelle de m par rapport à sa distribution. Ainsi, M doit être suffisamment grand pour que :

$$N(m)(N(u') + N(v')) \ge \sqrt{M} \tag{1.28}$$

ce qui se réécrit ainsi :

$$M \ge \frac{256}{(N(u') + N(v'))^2} \tag{1.29}$$

Dans le cas de DES, cela nous conduit à une attaque utilisant au moins  $2^{52}$  paires clair/chiffré, qui révèle potentiellement deux bits de clé. Ce résultat est obtenu avec les deux boîtes S 7 et 8 (les autres paires de boîtes S sont nettement moins favorables à cette attaque). Avec  $2^{55}$  paires clair/chiffré ou plus, la probabilité de succès de cette attaque (c'est-à-dire, deviner correctement deux bits indirects de la clé) dépasse 50%. Il serait tentant d'utiliser les mêmes couples clair/chiffré pour attaquer d'autres paires de boîtes S voisines, mais les autres paires nécessitent une quantité bien plus importante de textes clairs connus.

Comme la recherche exhaustive de la clé nécessite seulement  $2^{56}$  essais au pire (et  $2^{55}$  en moyenne), cette attaque ne remet pas en cause la sécurité de DES.

## 1.4.2 L'attaque améliorée

En 1994, Eli Biham et Alex Biryukov ont présenté au congrès Eurocrypt[7] une amélioration de l'attaque de Davies et Murphy. L'idée est relativement simple : plutôt que d'attaquer 16 tours de DES, mieux vaut en attaquer seulement 14. Il s'avère que chaque couple clair/chiffré fournit l'entrée des fonctions de confusion du premier et du dernier tour ; l'entrée de deux boîtes S se calcule à partir de cette entrée en « devinant » 12 bits de clé.

L'attaque améliorée se déroule comme suit :  $2^{12} = 4096$  attaques sont menées de front, chacune travaillant sur une combinaison possible des 12 bits de clé intervenant dans l'entrée des boîtes S 7 et 8 du premier tour. Chacune de ces attaques est une hypothèse sur la clé utilisée effectivement ; l'attaque sera plus probante sur l'instance de DES qui correspond à la clé effectivement utilisée. Ainsi, pour chaque instance, la déviation du motif de 8 bits est mesurée par rapport à une distribution uniforme ; l'instance qui fournit la meilleure déviation est considérée comme étant celle qui a travaillé sur les 12 vrais bits de clé. Cette attaque révèle le bit de parité (comme dans l'attaque de Davies et Murphy) et également 12 autres bits. Les mêmes couples

clair/chiffré peuvent servir pour l'attaque duale, où cette fois-ci ce sont les 12 bits de clé servant dans l'entrée du dernier tour qui sont devinés. Au total, avec  $2^{52}$  paires clair/chiffré, cette attaque peut retrouver 26 bits de clé avec une probabilité de succès d'environ 53%.

On peut affiner cet algorithme en classant les candidats suivant l'importance de la déviation mesurée; ceci augmente le coût de la recherche exhaustive finale nécessaire pour retrouver le reste de la clé, puisque plusieurs candidats devront être essayés. Si on considère que les couples clair/chiffré et les chiffrements devant être essayés par l'attaquant représentent la même complexité, alors le meilleur compromis est atteint avec  $2^{50}$  paires clair/chiffré et un coût calculatoire de  $2^{50}$  chiffrements DES, pour une probabilité de succès de l'attaque de 51%.

Cette attaque améliorée n'est pas non plus une menace sur la sécurité de DES, à cause du grand nombre de couples clair/chiffré nécessaires. Cependant, on peut conserver l'idée que le premier et le dernier tour de chiffrement peuvent être « éliminés », c'est-à-dire que la sécurité se mesurera sur deux tours de moins (donc 14 tours dans le cas de DES). La meilleure attaque connue à ce jour sur DES, à savoir la cryptanalyse linéaire de Matsui[62, 63], travaille également sur 14 tours, en « devinant » exhaustivement certaines parties de la clé sur le premier et le dernier tour.

## 1.4.3 Formalisation de l'attaque

L'attaque de Davies et Murphy peut se formaliser dans un cadre plus général; on peut alors établir un critère de sécurité qui donne une résistance prouvée à cette attaque. Ce travail à été présenté au congrès Asiacrypt'98[70].

On considère un schéma de Feistel à r tours (on supposera r pair, par soucis de simplification); la fonction de confusion du tour i est notée  $f_i$ , et n bits de la sortie des  $f_i$  forment un motif de  $2^n$  valeurs possibles qui peuvent suivre q distributions différentes (quoique proches de la distribution uniforme) qui dépendent du matériel secret (la clé) utilisé au tour concerné. Chaque distribution sera représentée par un vecteur dans  $\mathbf{R}^{2^n}$ , comme précédemment.

Pour chaque couple clair/chiffré, nous pouvons calculer le OU EXCLUSIF de r/2 de ces motifs de n bits. Cette valeur a une certaine distribution qui dépend de plusieurs bits de clé; nous pouvons calculer les différentes distributions possibles, et pour chacune l'information correspondante sur la clé. L'attaque consiste en l'utilisation de nombreux couples clair/chiffré afin de déterminer la distribution de ce OU EXCLUSIF et d'obtenir ainsi l'information correspondante sur la clé.

À chaque étage, il ne peut y avoir que q distributions possibles. L'opération OU EXCLUSIF étant commutative, seul compte au total le nombre de

chaque type de distributions. Il y a r/2 étages, donc le nombre de combinaisons possibles est :

$$\binom{r/2+q-1}{q-1} \tag{1.30}$$

Dans la pratique, certaines de ces combinaisons peuvent être identiques; par exemple, dans le cas de DES, il n'y a au final que deux distributions différentes.

Nous allons maintenant utiliser une nouvelle représentation des distributions : un vecteur distribution de  $\mathbf{R}^{2^n}$  peut être représenté par une fonction de  $\mathbf{Z}_2^n$  dans  $\mathbf{R}$  qui associe à un vecteur de n bits la coordonnée correspondante du vecteur distribution. Sur une telle fonction, on peut appliquer la transformée de Walsh-Hadamard-Fourier.

#### Transformée de Walsh-Hadamard-Fourier

La transformée de Walsh-Hadamard-Fourier[76] est en fait une représentation d'une fonction dans la base de Fourier, que l'on définit ainsi : c'est l'ensemble des fonctions  $v_y$ , pour y dans  $\mathbf{Z}_2^n$ , définies ainsi :

$$v_y: \mathbf{Z}_2^n \longrightarrow \mathbf{R}$$

$$x \longmapsto (-1)^{y \cdot x}$$

(1.31)

où  $y \cdot x$  est le produit scalaire de y et de x (c'est-à-dire le nombre de bits à 1 dans  $y \wedge x$ , où  $\wedge$  désigne le ET logique bit à bit).

Les coefficients de Fourier d'une fonction a de  ${\bf Z}_2^n$  dans  ${\bf R}$  sont calculés comme suit :

$$\hat{a}(y) = \sum_{x} a(x)v_y(x) \tag{1.32}$$

pour tout y dans  $\mathbb{Z}_2^n$ . On peut retrouver a à partir de  $\hat{a}$  en appliquant la transformation de Fourier inverse :

$$a(x) = 2^{-n} \sum_{y} \hat{a}(y) v_{y}(x) = 2^{-n} \hat{a}(x)$$

(1.33)

pour tout vecteur x de  $\mathbb{Z}_2^n$ .

Dans le formalisme de Fourier, le OU EXCLUSIF de la sortie de deux étages du cryptosystème devient une convolution des deux distributions; en effet, si a représente la distribution d'un motif de n bits de la sortie de la fonction de confusion du premier étage, et b est la distribution du même motif de la sortie du second étage, alors la fonction c représentant la distribution du OU EXLUSIF des deux motifs est telle que, pour tout x vecteur de n bits :

$$c(x) = \sum_{y \oplus z = x} a(y)b(z) \tag{1.34}$$

Mais, comme l'addition dans  $\mathbb{Z}_2^n$  n'est autre que le OU EXCLUSIF bit à bit, et comme pour tout vecteur binaire x on a  $x \oplus x = 0$ , on peut réécrire cette équation ainsi :

$$c(x) = \sum_{y} a(x - y)b(y) \tag{1.35}$$

Une convolution de deux fonctions se calcule aisément sur les représentations en base de Fourier : il suffit en effet de multiplier deux à deux les coefficients. Dans les notations précédentes, cela s'exprime de la façon suivante :

$$\hat{c}(x) = \hat{a}(x)\hat{b}(x) \tag{1.36}$$

Nous allons prouver un résultat similaire pour les déviations des distributions par rapport à la distribution uniforme. Pour une distribution représentée par la fonction a, nous notons a' la fonction telle que, pour tout x, on ait  $a(x) = 2^{-n} + a'(x)$ . Si c est le produit de convolution de a et b, alors c' est le produit de convolution de a' et b'. En effet, si on note d la fonction constante égale à  $2^{-n}$ , ses coefficients de Fourier  $\hat{d}(x)$  valent 1 si x = 0, et 0 sinon. Nous avons alors les équations suivantes :

$$\hat{a} = \hat{a}' + \hat{d} \tag{1.37}$$

$$\hat{b} = \hat{b}' + \hat{d} \tag{1.38}$$

$$\hat{c} = \hat{c}' + \hat{d} \tag{1.39}$$

$$\hat{c} = \hat{a}\hat{b} \tag{1.40}$$

De ces équations on déduit :

$$\hat{c}' + \hat{d} = \hat{a}'\hat{b}' + \hat{d}^2 + \hat{d}(\hat{a}' + \hat{b}') \tag{1.41}$$

Comme  $\hat{d}(x)$  ne peut valoir que 0 ou 1, nous avons clairement  $\hat{d}^2 = \hat{d}$ ; par ailleurs, nous avons  $\hat{a}'(0) = \hat{b}'(0) = 0$ , car pour toute fonction u,  $\hat{u}(0)$  est égal à la somme des u(x) pour tout x dans  $\mathbf{Z}_2^n$ , somme qui vaut 0 dans le cas de a' et b'. En intégrant ces résultats dans l'équation 1.41, on obtient :

$$\hat{c}' = \hat{a}'\hat{b}' \tag{1.42}$$

#### Résistance à l'attaque de Davies et Murphy

Afin de trouver une borne minimale à la complexité de l'attaque de Davies et Murphy, nous allons expliciter une borne maximale de la déviation du motif de la fonction de confusion f par rapport à la distribution uniforme. En effet, la distribution de sortie que nous pouvons mesurer à l'aide de couples

clair/chiffré n'est qu'une mesure de cette distribution, qui est d'autant plus fine que nous avons beaucoup d'exemples. Pour que l'attaque fonctionne, la déviation à mesurer ne doit pas être masquée par les fluctuations naturelles d'une mesure autour de son espérance.

Dans la suite, nous considérons M couples clair/chiffré, et le vecteur m dans  $\mathbb{Z}_2^n$  où  $m_i$  est le nombre de couples clair/chiffré tels que le OU EXCLUSIF des motifs de n bits des fonctions de confusion des r/2 étages pairs ait la valeur binaire i. Le vecteur m/M est une approximation de la distribution théorique pour une fonction de chiffrement « parfaite », c'est-à-dire indistinguable d'une permutation aléatoire de l'espace des messages clairs dans l'espace des messages chiffrés (nous utilisons ici la représentation d'une distribution par un vecteur dans  $\mathbb{R}^{2^n}$ ).

En norme euclidienne, la déviation « naturelle » de m par rapport à son espérance est de l'ordre de  $\sqrt{M}$  (cf. section 1.4.1). On utilise à nouveau la méthode du maximum de vraisemblance; si Y est un majorant de la déviation dans  $\mathbf{R}^{2^n}$  des distributions possibles du motif par rapport à la distribution uniforme, alors 2Y sera un majorant de la norme de la différence de deux distributions (par inégalité triangulaire), et on pourra dire qu'une attaque n'a de chances raisonnables de succès que si :

$$2Y\frac{M}{2^{n/2}} \ge \sqrt{M} \tag{1.43}$$

ce qui peut se réécrire ainsi :

$$M \ge \frac{2^n}{4V^2} \tag{1.44}$$

On notera que ce résultat utilise les même approximations que celles utilisées dans la description de l'attaque originelle de Davies et Murphy (section 1.4.1); en particulier, n doit être suffisamment grand pour que  $2^{-n}$  soit négligeable devant 1.

Nous pouvons obtenir ce majorant Y en fonction des coefficients de Fourier de la fonction de distribution du motif considéré. En effet, la norme euclidienne dans  $\mathbf{R}^{2^n}$  n'est autre que la norme  $L^2$  dans l'espace des fonctions de  $\mathbf{Z}_2^n$  dans  $\mathbf{R}$ , et le produit scalaire de deux fonctions a et b est :

$$a \cdot b = \sum_{x} a(x)b(x) \tag{1.45}$$

La base de Fourier  $(v_y)$  est une base orthogonale selon ce produit scalaire, et tous les  $v_y$  ont  $2^{n/2}$  comme norme  $L^2$ ; les coefficients de Fourier sont les

produits scalaires de la fonction avec les vecteurs de cette base. Donc, si a' est une fonction de  $\mathbb{Z}_2^n$  dans  $\mathbb{R}$ , sa norme  $L^2$  est :

$$N(a') = 2^{-n/2}N(\hat{a}') \tag{1.46}$$

On peut donc écrire :

$$N(a') \le 2^{n/2} \max_{x} |\hat{a}'(x)| \tag{1.47}$$

ce qui nous donne notre majorant Y:

$$Y = 2^{n/2} \max_{x} |\hat{a}'(x)| \tag{1.48}$$

où a' est la déviation par rapport à la distribution uniforme du motif de n bits dans le OU EXCLUSIF des sorties de r/2 étages du chiffrement.

Les coefficients de Fourier de la distribution du OU EXCLUSIF de r/2 motifs s'obtiennent en multipliant terme à terme les coefficients de Fourier des distributions des r/2 motifs, donc, si  $\mu$  est le plus grand (en valeur absolue) des coefficients de Fourier de la distribution du motif en sortie d'un étage, le plus grand des coefficients de Fourier de la distribution du motif sur r/2 étages sera  $\mu^{r/2}$ .

On obtient donc le critère de sécurité suivant :

- Calculer les coefficients de Fourier de la fonction représentant la déviation par rapport à la distribution uniforme de la distribution du motif choisi dans la sortie de la fonction de confusion de chaque étage. Dans le cas de DES, cela est effectué par énumération des entrées possibles de deux boîtes S voisines.

- Prendre le plus grand de ces coefficients en valeur absolue; on le note  $\mu$ .

- Le nombre de couples clair/chiffré nécessaires à l'attaque de Davies et Murphy sur le motif choisi est au moins égal à :

$$\frac{1}{4u^r} \tag{1.49}$$

La sécurité globale du schéma est donc ramenée à l'énumération des motifs pouvant présenter un biais par rapport à la distribution uniforme. Dans le cas de DES, en utilisant le même motif que Davies et Murphy (la sortie de deux boîtes S voisines), le critère donne une sécurité de l'ordre de  $1, 5 \times 2^{52}$ , ce qui rejoint les conclusions de Davies et Murphy (c'est-à-dire que le critère donne une valeur pertinente).

#### Approximations et sécurité réelle

Au cours de l'analyse décrite précédemment, un certain nombre d'approximations ont été faites. La plus importante d'entre elles est la majoration de la différence entre deux distributions en mesurant la différence entre chaque distribution et la distribution uniforme, et en appliquant l'inégalité triangulaire. Dans le cas de DES, il n'y a que deux distributions possibles, symétriques par rapport à la distribution uniforme, aussi l'inégalité triangulaire devient, dans ce cas précis, une égalité. Pour ce qui est d'autres schémas, cette méthode peut amener à calculer un critère de sécurité plus faible que la sécurité réelle (ce qui revient à dire qu'il s'agit d'un critère de sécurité et non d'une attaque).

Les autres calculs sont également sujets à des approximations :

- Nous avons considéré que les  $2^n$  coordonnées du vecteur m sont des variables indépendantes entre elles, ce qui n'est pas vraie, puisque leur somme est toujours M. Dans le cas de DES, on travaille sur des motifs de 8 bits, donc il y a 256 coordonnées; aussi nous pouvons négliger cet effet.

- Les variables  $m_i$  ne suivent pas, en fait, une loi normale, mais une loi binômiale qui s'approche d'une loi normale quand M devient grand, par application du théorème central limite. Dans la pratique, cette distinction n'a pas lieu d'être dès que M est supérieur à quelques milliers.

- La déviation du motif mesuré par rapport à la distribution uniforme est supposée petite, ce qui est de toutes façons une caractéristique très souhaitable d'un système de chiffrement symétrique, qui est censé être indistinguable computationnellement d'une permutation aléatoire.

Dans la section 1.4.2, nous avons vu comment l'amélioration de l'attaque par Eli Biham et Alex Biryukov[7] permet une attaque plus rapide en traitant séparément le premier et le dernier tour. L'applicabilité d'une telle méthode dépend des détails de la fonction de confusion utilisée dans ces deux tours et est difficile à formaliser; une étude de sécurité ne devrait donc appliquer le critère de résistance à l'attaque de Davies et Murphy que sur les tours intérieurs. Autrement dit, il faut rajouter deux tours « de sécurité ».

La recherche et l'énumération des motifs potentiellement « dangereux » reste un problème ouvert. Davies et Murphy ont également étudié dans leur article[26] les motifs offerts par trois boîtes S voisines, mais ces motifs ne donnent pas de meilleure attaque. En fait, si le triplet de boîtes S contient les boîtes 7 et 8, alors l'attaque résultante a la même efficacité que l'attaque sur les deux boîtes 7 et 8 seules; sinon, elle nécessite plus de couples clair/chiffré qu'il n'est possible d'en calculer (DES travaille sur des mots de 64 bits et ne peut chiffrer que 2<sup>64</sup> textes clairs différents).

# 1.5 Conclusion

Dans ce chapitre, nous avons étudié la sécurité du standard de chiffrement DES. Cet algorithme a été défini il y a plus de 25 ans et reste très employé de nos jours; nous allons voir, dans les chapitres suivants, comment DES et d'autres cryptosystèmes s'adaptent aux évolutions de la technique, que ce soit pour leur implantation ou leur cryptanalyse, en logiciel sur des processeurs génériques, ou sur du matériel spécialisé.

# Chapitre 2

# Implantations classiques sur processeurs génériques

## 2.1 Capacités des processeurs polyvalents

Depuis l'invention en 1971 par Intel du premier micro-processeur, le 4004, l'informatique n'a cessé de se concentrer sur le modèle de l'ordinateur polyvalent : doté d'un processeur central sans capacité particulière, et de périphériques génériques tels qu'un écran ou un stockage de masse (bande magnétique, disque dur), il tranche avec les mainframes, énormes systèmes centralisés qui ont fait la gloire de la décennie précédente. Des systèmes tels que la série des fameux PDP de Digital géraient des dizaines de terminaux et hébergeaient autant de sessions interactives. Les processeurs étaient souvent épaulés par un support matériel évolué de cet environnement particulier, afin de conserver la réactivité de toutes ces interfaces.

A contrario, l'ordinateur « personnel », destiné à servir à un seul utilisateur à la fois, est construit autour d'un processeur unique, dans une architecture dépouillée; tout est fait en logiciel. Le comble de ce centralisme sera atteint avec le ZX81 de Sinclair, dont le processeur central est requis pour la génération du signal vidéo envoyé à l'écran (ce qui l'amputait de la majorité de sa puissance de calcul). Ce modèle s'est tellement imposé sur le marché, depuis l'explosion de l'informatique « familiale » (au début des années 1980), que désormais les remplaçants des mainframes, devenus serveurs de calcul, disque, Web ou autres protocoles réseaux, sont des ordinateurs personnels flanqués d'un peu plus de mémoire et de disques durs plus gros et plus fiables.

Quant aux matériels embarqués, notamment les cartes à puces, ils sont essentiellement des répliques des micro-ordinateurs personnels qui se fabriquaient dix à quinze ans auparavant, dans un emballage rendu compact par le progrès technologique. Nous allons détailler les capacités et performances de ces matériels et nous verrons comment leur structure interne conditionne l'efficacité de certains algorithmes cryptographiques.

## 2.1.1 Les processeurs 8 bits

Si le 4004 traitait les informations par blocs de 4 bits, ses successeurs se sont rapidement adaptés à l'octet, qui est devenu l'unité standard de groupement des données; en effet, l'octet peut prendre 256 valeurs différentes, ce qui permet de coder un jeu de caractères suffisamment étendu pour englober différentes variations typographiques, notamment les caractères accentués des différentes langues d'Europe occidentale. Les mots de 7 bits, suffisants pour le codage ASCII (qui ne comporte pas d'accent, mais l'anglais peut s'en passer), ont longtemps été utilisés pour la télématique, et laissent encore maintenant des traces durables (par exemple, quand on envoie un courrier électronique en français, si ce courrier doit traverser divers serveurs d'outre-atlantique, il peut y perdre ses accents); mais l'octet devient la norme. De façon assez amusante, le monde occidental s'éveille à la présence d'autres écritures, et le nouveau standard d'encodage des caractères, l'Unicode, travaille avec des mots de 16 bits; comme l'octet est parti pour durer, le consortium Unicode et l'ISO ont mis au point un codage de taille variable compatible avec le codage ASCII, l'UTF-8. Nous pouvons tenir pour acquis que tous les processeurs génériques conçus dans les prochaines années sauront adresser des octets efficacement.

Les premiers micro-processeurs, et toute la lignée de ce qu'on appelle couramment les processeurs « 8 bits », accèdent à la mémoire octet par octet et travaillent sur des valeurs de même taille. Le cœur du chemin de données est un registre appelé accumulateur. Ce registre est une mémoire de la taille d'un octet ; les instructions élémentaires sont classables dans les catégories suivantes :

- accès mémoire,

- instructions arithmétiques et logiques,

- contrôle de flux.

Les opérations de contrôle de flux sont les branchements conditionnels et les opcodes d'appel de fonction (avec sauvegarde de l'adresse de retour). Les instructions arithmétiques sont les opérations mathématiques simples telles que l'addition, la soustraction, la négation (qui se fait couramment par complémentation à deux). La multiplication, opération plus complexe, n'est apparue que sur des variantes tardives des processeurs 8 bits, telles que le 8080 d'Intel, ou le 6809 de Motorola. Les instructions logiques sont les

opérations binaires sur les valeurs : OU logique bit à bit, décalages, etc.

La gestion des accès mémoire est la partie la plus complexe du processeur; elle utilise un ou plusieurs registres d'adresse, sur lesquels les opérations arithmétiques et logiques ne sont pas possibles directement, mais qui sont manipulables par les modes d'adressage. Les modes d'adressage sont les moyens plus ou moins complexes d'exprimer l'adresse d'un octet comme variation sur le contenu des registres d'adresse et de certaines zones mémoires désignées par ces mêmes registres.

Prenons comme exemple un processeur 8 bits « avancé », le 6809. Ce processeur, dû à Motorola, a équipé la famille des MO5 et TO7, fer de lance du plan « Informatique pour tous » du milieu des années 1980. L'ancêtre direct du 6809, le 6805, équipe un grand nombre de cartes à puce bas coût. Le 6809 dispose des registres suivants :

- deux accumulateurs 8 bits, A et B. Ensemble, ils forment le registre D, de 16 bits.

- deux registres d'adresse génériques, X et Y, de 16 bits. Le 6809 peut adresser 65536 octets différents, soit 64 Ko.

- deux registres d'adresse spéciaux, U et S, de 16 bits, qui sont utilisés dans les opcodes de gestion de pile que le 6809 possède nativement.

- un registre de page, DP, de 8 bits; c'est en fait un demi-registre d'adresse, qui emporte les 8 bits de poids fort de l'adresse; cela permet de gérer les opcodes ne spécifiant que les 8 bits de poids faible, et, dans une certaine mesure, de fabriquer du code déplaçable en mémoire.